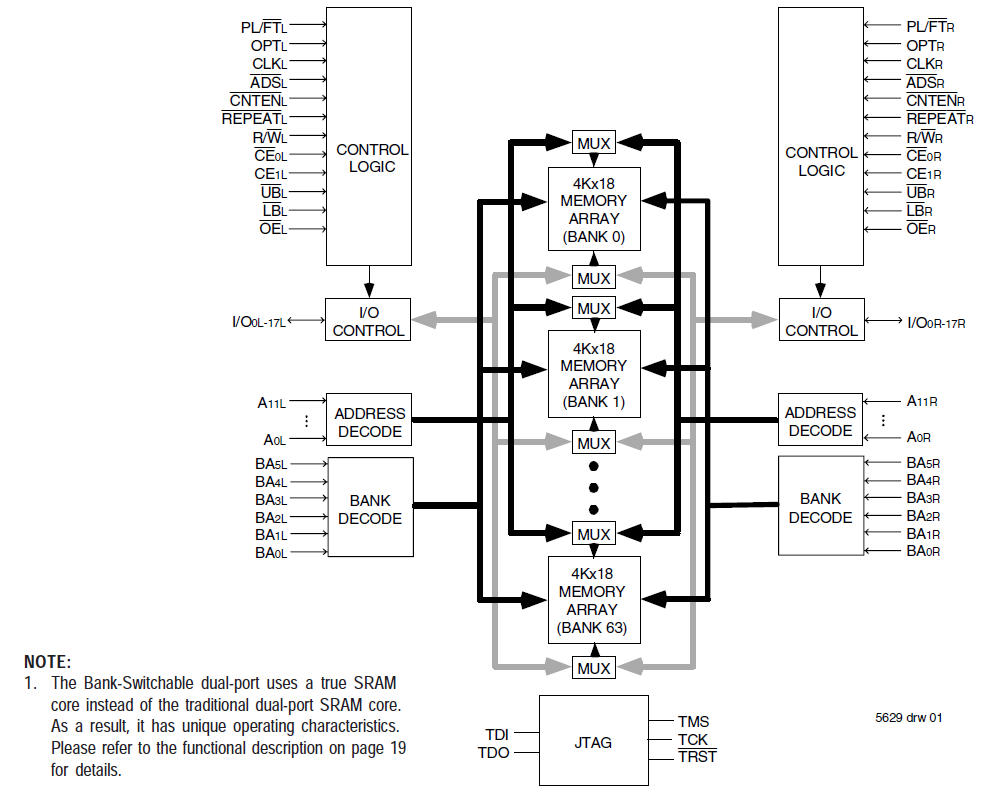

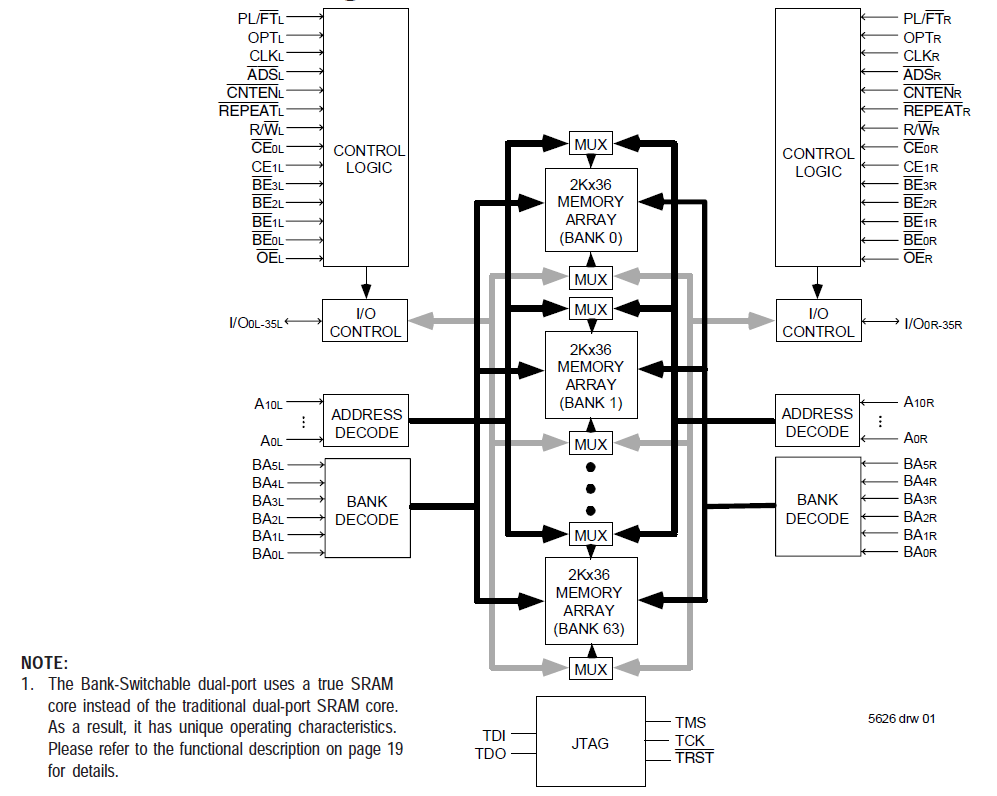

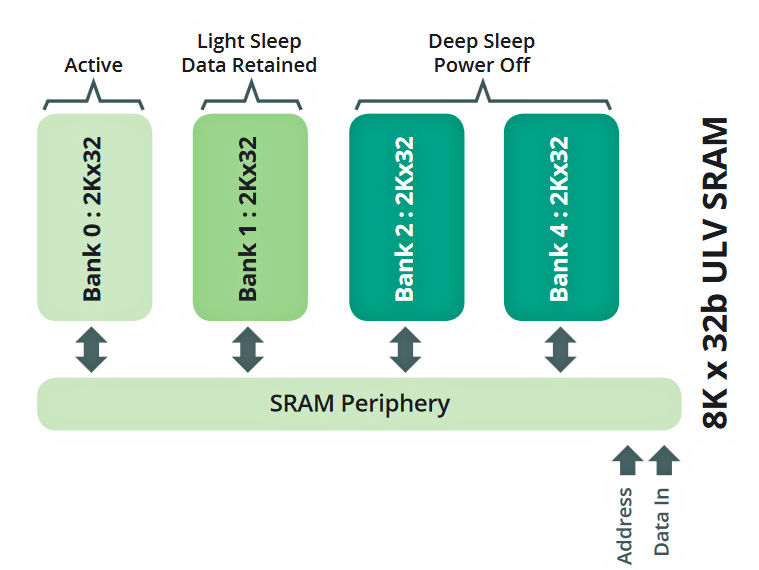

a) Memory bank construction using single-port SRAMs and (b) proposed... | Download Scientific Diagram

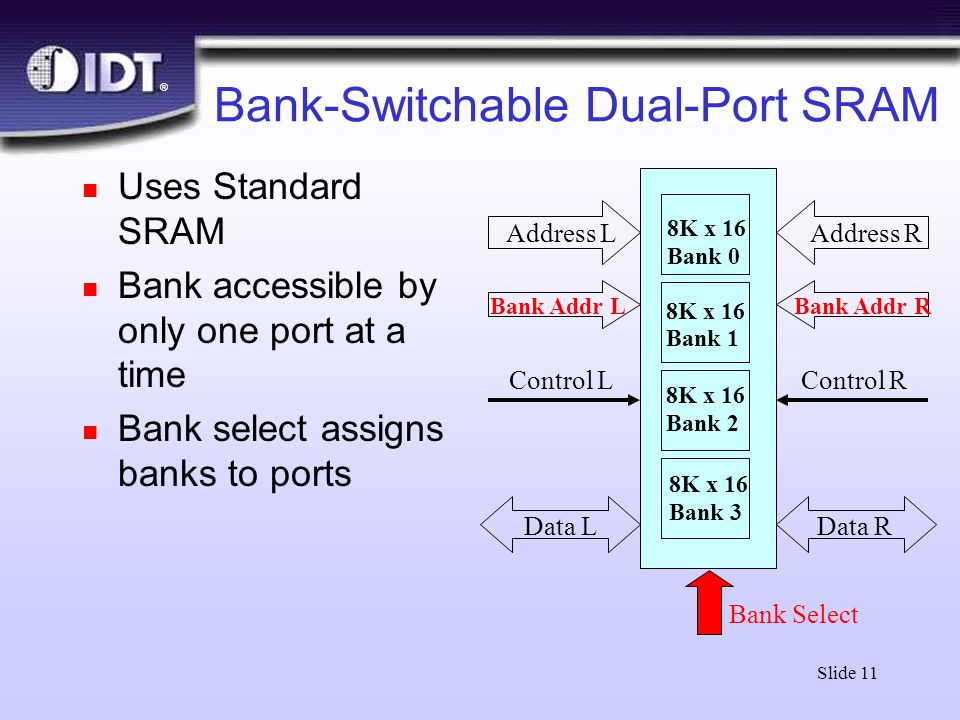

Multi-Port SRAM Overview. ® Slide 2 Objectives n What are Multi-Port SRAMs? n Why are they needed? n Arbitration Features l Busy l Interrupt l Semaphore. - ppt download

Multi-port SRAM with Multi-bank for Self-organizing Maps Neural Network (Invited paper) | Semantic Scholar

Figure 1 from A 0.6-Tbps, 16-port SRAM design with 2-stage- pipeline and multi-stage-sensing scheme | Semantic Scholar

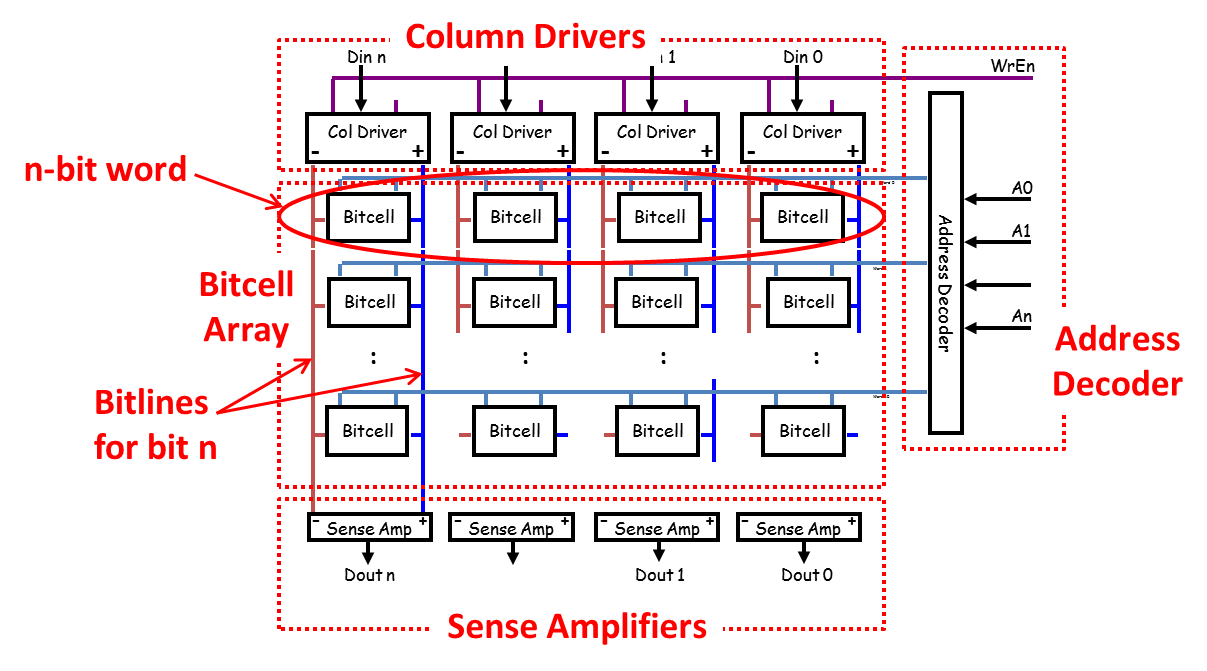

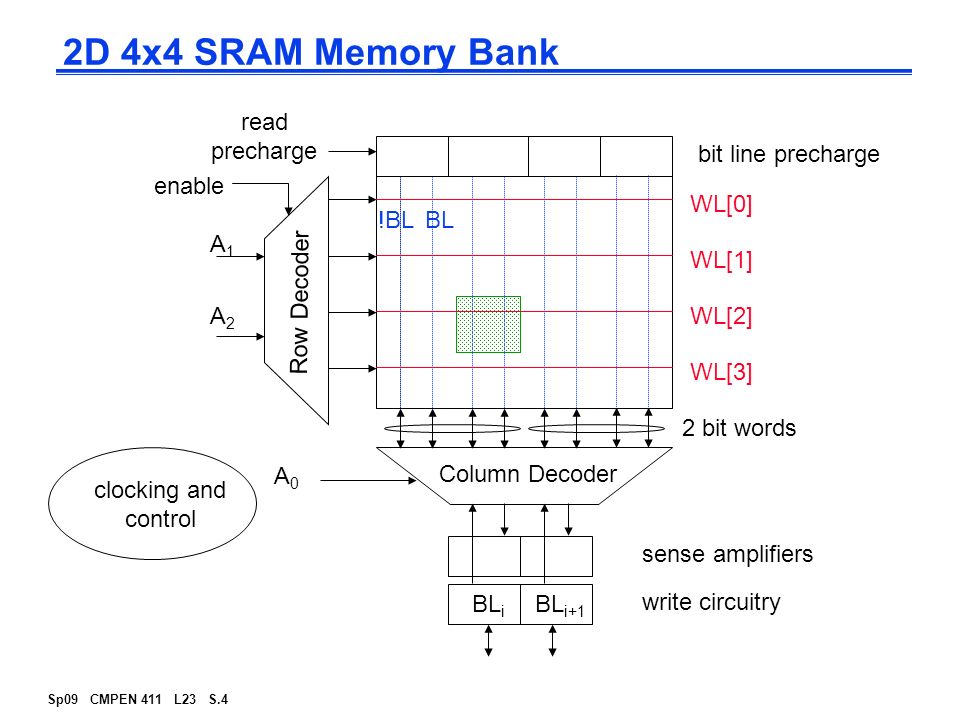

Sp09 CMPEN 411 L23 S.1 CMPEN 411 VLSI Digital Circuits Spring 2009 Lecture 23: Memory Cell Designs SRAM, DRAM [Adapted from Rabaey's Digital Integrated. - ppt download

Multi-port SRAM with Multi-bank for Self-organizing Maps Neural Network (Invited paper) | Semantic Scholar

Figure 5 from A 0.6-Tbps, 16-port SRAM design with 2-stage- pipeline and multi-stage-sensing scheme | Semantic Scholar

Multi-port SRAM with Multi-bank for Self-organizing Maps Neural Network (Invited paper) | Semantic Scholar